CMOS电路ESD保护结构设计方法

1. CMOS工艺简介

CMOS(互补式金属氧化物半导体)是一种在硅质晶圆上集成互补NMOS与PMOS器件的工艺。随着技术发展,电路尺寸不断缩小、栅氧化层变薄。为了应对因芯片面积增加而外围环境(如ESD应力)相对不变的问题,需要优化其静电放电(ESD)保护器件的性能。

2. ESD保护原理

ESD保护电路的核心作用是在芯片引脚间建立低阻旁路路径,将瞬时的大静电电流导向电源线(VDD/VSS),同时箝位电压,从而防止内部工作电路因过压、过流而损坏。对保护结构的关键要求在于:能够快速响应(快速触发)瞬态ESD事件但自身不发生损坏;在ESD事件期间提供稳定有效的保护;并将正常工作时的附加影响(如信号输入延迟的增加、电容负载的增加)控制在可接受范围内,同时还必须确保在正常加电工作期间不会意外触发。

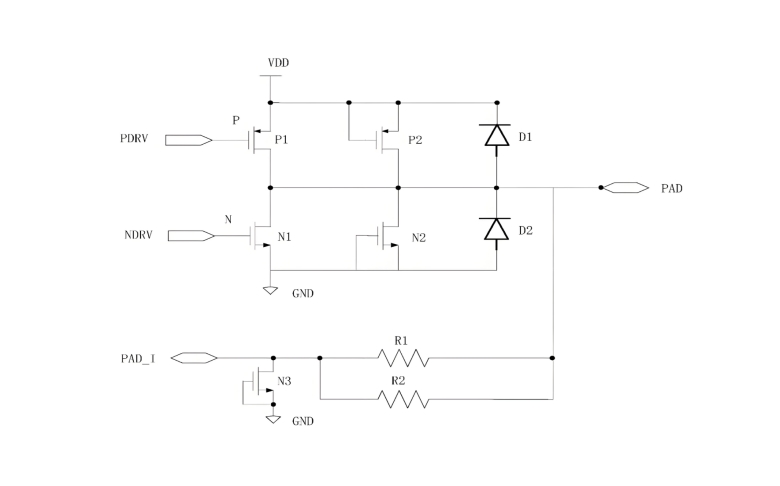

3. CMOS ESD保护结构设计

ESD电流直接来自外部输入/输出(I/O)引脚,因此保护结构通常位于PAD(焊盘)旁边或集成在I/O电路内部。典型的I/O电路包含输出驱动部分和输入接收器。所有与PAD直接相连的内部器件都需要设计一条低阻旁路(可以利用电阻、二极管、双极性晶体管或MOS管等途径)将电流有效地分散至芯片的电源(VDD)和地(VSS)管脚。其中,NMOS器件由于其良好的CMOS工艺兼容性以及寄生n-p-n晶体管能够吸收大电流的特性,常被用作栅极接地NMOS(GGNMOS)保护结构。需特别注意的是:当漏极-衬底结发生雪崩击穿时产生的电子-空穴对,可能会引发碰撞电离导致局域电流密度过大,从而造成器件本身的损坏。

【推荐阅读】

- 2025-08-01CMOS电路ESD保护结构设计方法

- 2025-07-31共模电感选型:材料与参数平衡

- 2025-07-30ESD二极管结构差异与选型指南

- 2025-07-29静电威胁电子产品的重要特性:从隐蔽到复杂

- 2025-07-26实用蓝牙耳机ESD防护方案与元器件选型建议

- 2025-07-25通信端口与I/O口静电防护的高分子ESD解决方案

【本文标签】:CMOS电路设计 ESD保护结构设计 ESD保护二极管 保护电路设计 深圳阿赛姆

【责任编辑】:ASIM版权所有:http://www.asim-emc.com

转载请注明出处

全程EMC技术支持

全程EMC技术支持 在线微信客服

在线微信客服